2025电赛总结

随着电赛落下帷幕,也获得了国二的成绩,感觉还是有很多不足,所以来写个文章记录和反思一下。

题目

解题思路

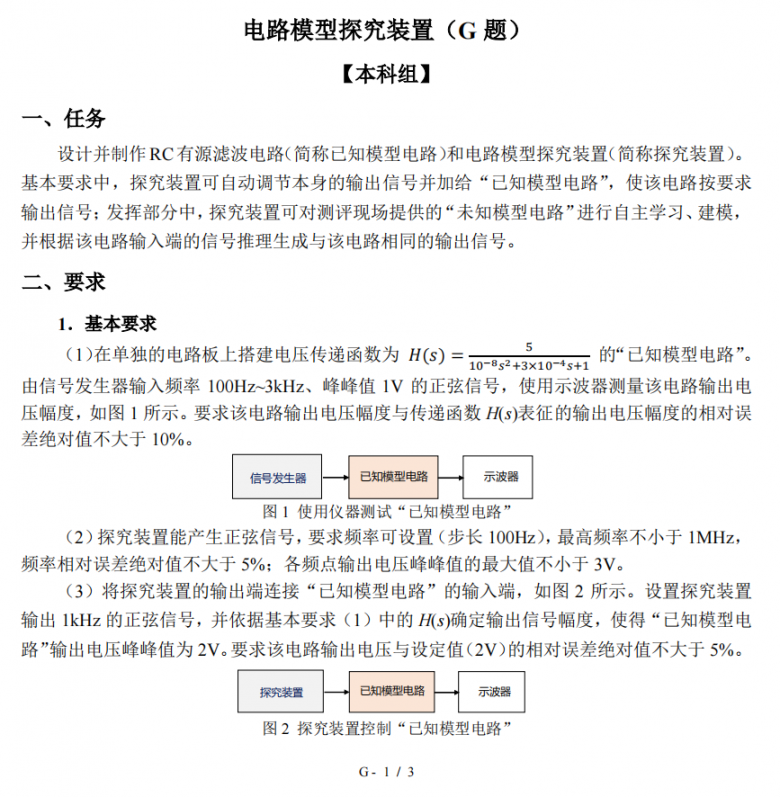

首先是基础部分第一问,只是按要求做出来一个指定的滤波器,题目中给了传递函数,这是一个二阶低通滤波器,增益为5,截止频率在1.6Khz左右,Q值为0.33,通过仿真确定参数和模型搭出来就好。

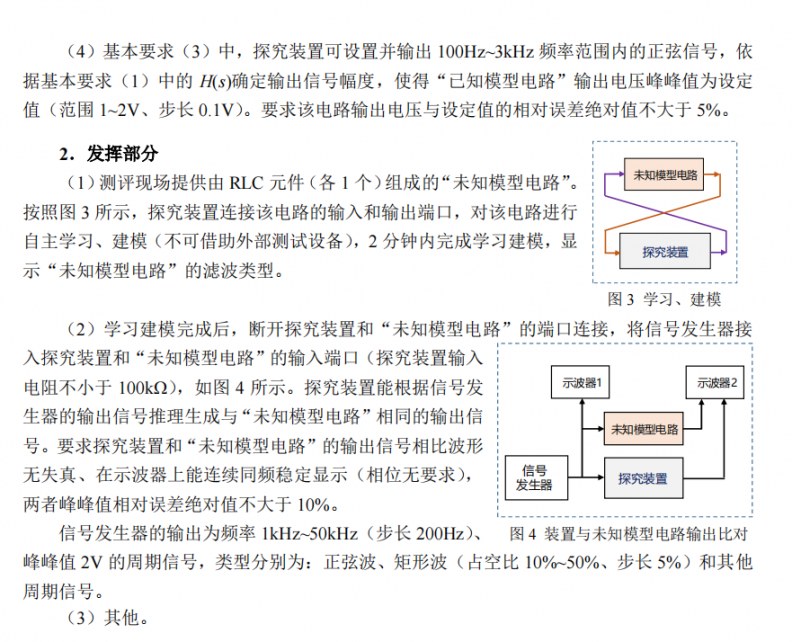

接下来,纵观题目要求,整体要求就是通过数字方式实现一个滤波器,然后根据要求设定输入或者输出。后面要求输出自定义波形,所以这里不能使用DDS,使用dac是最好的方案,但是需要软件功底足够。系统输出要求峰峰值不小于3V,但是如果滤波器增益比较小,那输出可能就无法达到要求,所以保险起见使用正负10V的DAC,频率方面要求波形频率50khz,那DAC的频率最低250khz,而且这样一个周期才只有5个点,而且后边需要扫频,建议频率在满足幅值要求下越高越好,AD方面,建议与DAC相互匹配,差距不要过大就好。

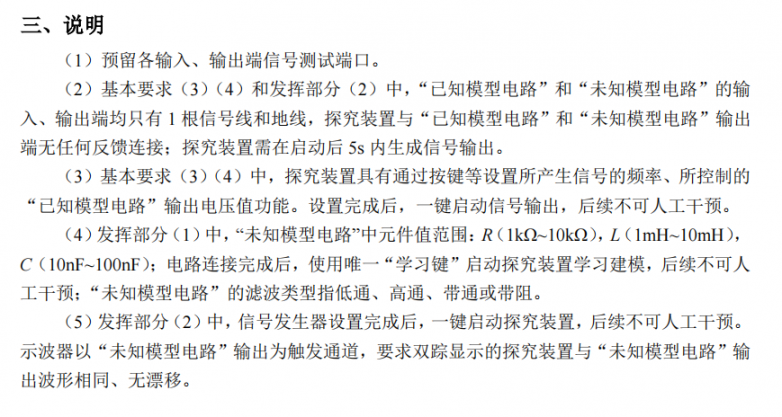

系统方面,我们使用的是STM32和FPGA组合的方案,原因是FPGA外挂ADC和DAC比较方便,而且可以满足频率要求,如果用32外挂的话,在这类ADDA都是并口,就算使用FMC总线也没法同时跑满两块设备。而且对于FPGA的逻辑资源占用也不是很高,只需要驱动ADDA以及和stm32通信就好。不过需要注意的是,dac需要自定义输出波形,先通过STM32发送一个波形数组,然后设定输出频率和幅值就好。

在软件部分,其实只要将发挥部分做出来,基础部分第三第四小问也就直接解决了,其实题目通篇一直在说明的就是传递函数,根据信号与系统,信号可以在时域处理,也可以在频域或者S域(Z域)处理,所以也就出来三种方案,首先是测量滤波器的传输特性,最直观的方法就是直接扫频,然后得出幅频响应和相频响应,然后可以计算出滤波器的传递函数,在用传递函数得出滤波器响应波形并输出,时域使用FIR,频域使用傅里叶变换然后在频域乘积,S域则需要双线性变换。

如果采用时域FIR,则需要先扫频然后得到响应,再从响应反向推导出滤波器类型和参数,在根据参数确定FIR滤波器的系数,这就要求对于FIR滤波器的计算过程以及滤波器的类型也了如指掌,但是这样求出来的应该是理想滤波器,也就是如果给定滤波器在某一个频率响应出现了偏差,就可能误差过大。

如果采用频域滤波,这里则是通过滤波器扫频得到滤波器的响应曲线,然后在频域和响应曲线做乘法就可以得到输出幅值,在通过逆向FFT后DAC输出。但是如果目标信号包含多个频率分量,那还需要测量滤波器的相位响应,否则波形合成时不同分量的相位差会发生变化导致波形不符合。

如果采用S域则是通过双线性变化然后进行滤波,但是同样时需要传递函数。不过这样的计算量比较大。

笔者最后采用的方案是频域滤波。首先通过扫频,对每个ADC采集回来的值做FFT运算,然后求出在扫描频率的幅度响应和频率响应,不过这里的格式其实可以直接使用FFT的结果,也就是向量,然后扫频过后就得到了每个频率的相应向量。当给出一个指定信号,并且ADC采集后进行FFT转换,直接用相应向量和FFT结果做向量乘积,在做逆向FFT就可以得到相应的波形。这样做的特点是所有相应都是实际测量出来的相应,即是好处也是坏处。好的点是更符合实际滤波器,坏处是对于AD和DA的要求比较高。最后在通过DAC输出,理论上只要按ADC的采样频率输出即可。

实际遇到的一些问题

傅里叶变换的截断、泄露和ADC的采集

根据奈奎斯特采样定理,只要adc采样频率大于目标频率的二倍,但是实际使用可能需要更高的倍数,4倍,8倍,而且在进行傅里叶变换时进行的周期性的延拓,所以会发生频谱泄露。解决方案就是首先测量目标频率,然后在已知频率的情况下进行采集,通过改变采样率,这样采集到的数据就是周期的整数倍,不会发生频谱泄露。

如何测量相位相应?

理论上来说,傅里叶变换的结果中包含相位信息,这里的相位信息来自于ADC开始采集的初始相位,所以一种方案是在扫频时,dac驱动模块在FPGA内部给ADC一个触发信号,adc在接收到触发信号后才开始采集,这样就可以得到滤波器的相位变化,但是,这里的相位变化是信号经过dac和adc以及中间一系列的环节造成的,也就是说这中间任何一环的相位波动都会导致这里采集到的相位信息发生变化。另一种方案是采用控制变量,使用双路dac和adc,一路经过滤波器一路经过滤波器,采集后求相位差,这里采集到的就是只有滤波器的相位信息,误差在于硬件误差,相对较小。

如何稳定同屏显示?

这里和以往的电赛题很相似,就是锁相的问题,但是由于系统框图,本系统只有一个输入端口和一个输出端口,所以锁相只能和输入信号锁相。那如何锁相呢?换句话说就是为什么会导致漂移,根本原因就是频率精确度不够,所以只要对频率进行微调即可。也就是说,采集两路信号并求相位差,然后求出相位差的变化率也就是频率差,在对频率进行修真就可以做到完美的锁相,瓶颈在于频率的分辨率。

如何得到高精度自定义频率?

由于系统是stm32+FPGA,所以可以使用FPGA的PLL得到高频信号,但是这只能得到固定的频率,如果需要自定义改变需要学习FPGA的原语,短时间内无法做到。所以只能将目光转向外部,可以外挂一块DDS,用它来输出方波给FPGA,这样ADC的采样率也可以做到很高精度。例如9833或者9834。